1、引言

近年来,随着自动化测试、结构健康监测、智能制造以及新能源装备等领域的快速发展,基于PXIe平台的数据采集系统在工程测试中的应用越来越广泛。PXIe作为一种开放、模块化、高带宽的测试与测量平台,具备以下典型优势:

- 总线带宽高、通道数易扩展,可满足多点、多物理量同时测试的需求;

- 模块形态灵活,可方便集成电压、电流、桥路、声学、振动等多种采集卡;

- 配合上位机软件和触发/时钟资源,可以实现复杂工况下的自动化测试。

在此背景下,测试数据不再是单通道、单点的简单记录,而是多通道、多传感器、多物理量之间的关联分析。这直接引出一个核心问题:如何保证各通道数据在时间上的严格对齐,即“同步”问题。

本文围绕“同一块 PXIe数据采集卡内部不同通道之间的同步”展开,先讨论数据同步的重要性、异步采集可能带来的后果,随后以PXIe采集卡为例,分析单板多通道同步的实现原理与基本方式。不同采集卡之间的同步问题将放在后续文章中单独讨论。

2、数据同步的重要性

2.1 多通道测试场景的需求

在实际工程项目中,多通道采集早已成为常态,例如:结构振动测试中,需要同步采集多个加速度传感器,用于模态分析、振型识别;电机与电力电子测试中,需要同时采集电压、电流、转速、扭矩等多种信号,用于效率分析和控制算法验证;声学与噪声测试中,需要同步采集多个麦克风阵列通道,用于声源定位和波束形成;机顶盒、通信设备等电子产品测试中,需要同步采集功耗、温度、控制信号等,用于关联分析和故障定位。

这些应用有一个共同特点:后续的数据处理往往基于多通道之间的时间关系,而不是某个通道的绝对值本身。典型如:计算相位差、传递函数、互相关函数;分析事件的时序,例如“某通道故障信号出现后,其他通道响应的时间延迟”;进行空间重建(阵列测量)、多传感器信息融合等。如果通道之间时间轴错位或漂移,即便单通道采样精度很高,整体测试结论仍然可能是错误的甚至是相互矛盾的。

2.2 从“采样率一致”到“采样时刻一致”

在实际工程交流中,容易出现一个误解:“只要多通道设置了相同的采样率,就是同步了。”实际上,同样是10 kS/s的采样率,如果每个通道各自有独立的时钟或独立启动,则采样时刻可以存在固定偏移,甚至在测试过程逐渐漂移。这种情况下,通道之间虽然“平均采样间隔”相同,但每一个采样点的时间戳并不一致,仍然属于异步采集。

真正意义上的多通道同步,至少包含两个层面:

- 统一时间基准:所有通道共享同一个时钟源或经过锁相后的同源时钟;

- 统一采样起点与采样节奏:各通道的采样在同一时刻开始,并由同一个“采样时钟”驱动。

只有同时满足上述条件,才能保证“同一个采样点序号 n,在所有通道上对应同一个物理时间 t”。

3、异步采集可能导致的问题

若在 PXIe 数据采集系统中,同一块采集卡的各通道未实现真正同步,将可能导致以下问题:

3.1 多通道相位与幅值分析偏差

在频域分析中,多通道之间的相位关系通常用于判断系统的相位响应、传递函数等。如果通道间存在时间偏移 Δt,则在频率 f 处将引入额外相位误差:

对于高频信号,即使微小的时间偏差,也会转化为明显的相位误差,进而导致:传递函数估计不准确;系统稳定性判断失误;模态分析结果偏离真实情况。在瞬态分析中,时间偏移还会导致同一事件在各通道上的峰值对齐失败,使得幅值峰值、上升沿等特征提取出现误差。

3.2 长时间测试中的时间漂移

如果各通道依赖非锁相时钟或非统一时钟源,随着测试时间增长,采样时钟的微小频率偏差会积累为明显的时间漂移。短时间内看似“差不多对齐”的波形,长时间后可能出现采样点序列明显分离,导致:无法将不同通道的数据在同一时间轴上进行长期趋势分析;长时间相关性分析(例如温度与功耗、振动与负载)失真;后处理阶段难以通过简单插值进行补救等问题。

4、基于 PXIe 的单板多通道同步基本原理

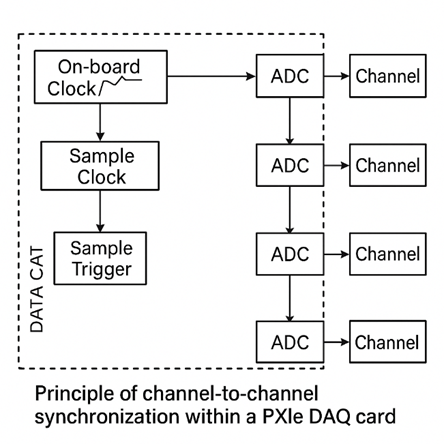

在PXIe体系中,一块多通道数据采集卡通常已经针对“单板多通道同步”进行了硬件和驱动层面的设计。其基本思想可以概括为:在同一块采集卡上,为所有通道提供统一的时间基准、统一的采样时钟和统一的启动触发,从而保证采样时刻完全一致。下面从几个关键方面进行解析:

4.1 统一时间基准(板载时钟/参考时钟)

PXIe采集卡通常拥有一个板载时钟(On-board Clock),例如由高稳定度晶振提供的基准频率(如 10 MHz、20 MHz 等)。同时,PXIe 机箱还可以通过背板提供系统参考时钟(如 10 MHz 参考时钟),供各模块锁相使用。对于单板多通道同步而言,一般有两种方式:

1. 全部通道共享同一块板载时钟:所有采样相关的时钟信号(如采样时钟、内部分频时钟等)均从同一个基准晶振分频/倍频得到;通道之间不存在各自独立的自由振荡器,从而避免了长时间运行中的相对漂移。

2. 采集卡锁相到机箱参考时钟:板载时钟通过锁相环(PLL)锁定到机箱提供的参考时钟;虽然这一机制更多用于多卡同步,但对单卡本身同样有利于提高整体时间基准的稳定性。

无论采用哪种方式,关键点是:采集卡内部所有通道使用的是“同源时钟”。同源时钟保证了采样周期在所有通道上完全一致,为下一步“统一采样时刻”打下基础。

4.2 统一采样时刻(共享采样时钟)

在有了统一时间基准之后,PXIe采集卡通常还会设计一个统一的采样时钟(Sample Clock),用于驱动该卡上的所有采样通道。其实现方式大致包括两类架构:

1. 多ADC同步采样架构(Simultaneous Sampling):每个通道配备独立的模数转换器(ADC),所有 ADC 由同一采样时钟驱动;在采样时刻 tnt_ntn,所有 ADC 同时对各自通道的模拟信号进行采样并输出数字结果;这种方式能够实现真正意义上的“逐点同时”采样,适用于对相位、瞬态特性要求较高的场景(振动、声学阵列等)。

2. 多路复用 + 单 ADC 架构(Multiplexed Sampling):多个通道通过模拟开关/多路复用器依次送入同一 ADC;整体采样周期由统一采样时钟控制,但各通道在一个采样周期内依次轮询;对于低频、缓变信号(如温度、电压慢变量等),可以认为“准同步”;但从严格意义上说,通道间仍存在固定时间偏移。

在工程实践中,若需要严谨的同步(尤其是相位分析、阵列测量),应优先选用支持同步采样、多 ADC 架构的 PXIe 采集卡,并在设计与选型阶段予以明确。

4.3 统一启动触发(Start Trigger)

即使所有通道共享同一个采样时钟,如果各通道在不同时间开始采集,仍然会出现时间轴上的固定偏移。因此,在PXIe系统中,采集卡通常提供统一的启动触发机制:在驱动配置中,将多通道归属于同一个“任务(Task)”;该任务在接收到一次“开始采集”的触发信号(Start Trigger)后,才会启动采样时钟并开始采样;由于任务内通道共享同一个触发源,所有通道的“第一个样本”对应的是同一时刻。这个触发信号既可以是:软件触发:上位机发出开始命令,驱动产生内部触发信号;硬件触发:由外部数字信号或某一路模拟信号的阈值事件触发。

对于单板多通道同步,一般推荐:尽量将所有需要同步的通道放在同一个采集任务中,避免多个任务分别启动造成不必要的时序差;若必须使用多个任务,也应确保这些任务共享同一个硬件触发源,并由同一采样时钟驱动。

度纬科技始终致力于在数据采集领域中实现创新、独特和可靠的产品方案。我们深知,这些要素是企业在市场竞争中立足的基石。正因为如此,我们将创新的灵感来源于客户的真实应用需求,而非仅仅为了展示华而不实的产品特性。通过不断优化和提升数据采集方案,度纬科技助力合作伙伴迈向高效精准的未来。欢迎选择度纬科技010-64327909,共同开启数据采集的新篇章。