In data acquisition systems (DAQ), bit depth and sampling rate are crucial parameters describing the performance of the Analog-to-Digital Converter (ADC). Bit depth refers to the number of binary bits used by the ADC to convert an analog signal into a digital signal. Sampling rate refers to the number of times per second the ADC samples the analog signal, typically expressed in "Samples Per Second" (SPS). For example, a sampling rate of 1,000 SPS means the ADC samples the signal 1,000 times per second. The sampling rate describes only the frequency of data extraction over time by the ADC and is independent of the input signal's voltage range.

Figure 1 Analog Signal Acquisition Flowchart

This article will explore the critical roles of bit depth and sampling rate in data acquisition systems, analyzing how they impact overall system performance, measurement accuracy, and signal capture capability. This will help readers better understand the importance of these parameters for system design.

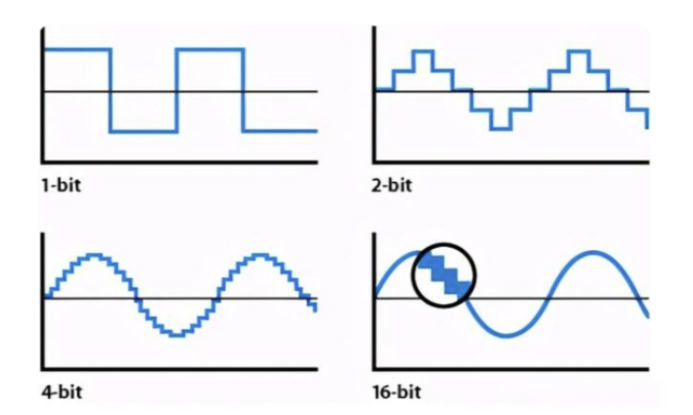

Bit depth plays a vital role in DAQ systems. The direct effect of increasing bit depth is a reduction in the system's quantization error. Each additional bit doubles the number of discrete voltage levels the ADC can represent, allowing it to convert the analog signal into a finer digital representation. For instance, a 16-bit ADC can discretize a signal into 65,536 levels, while a 12-bit ADC can only divide it into 4,096 levels. This means a 16-bit ADC can capture much smaller voltage changes during conversion, making it suitable for high-precision applications. High-bit-depth ADCs also excel at measuring weak signals; they can effectively identify faint signals and avoid significant noise interference. This characteristic allows the ADC to capture signal changes more precisely, thereby enhancing measurement accuracy and precision. Furthermore, as bit depth increases, quantization noise within the signal decreases proportionally, improving the Signal-to-Noise Ratio (SNR). This is particularly important for applications demanding high precision and high SNR, such as medical devices, precision measurement instruments, and seismic data acquisition.

Figure 2 Same Sine Wave Sampled at Different Bit Depths

It's important to note that while high bit depth offers higher precision, not all systems require extremely high bit depths. In some cases, environmental noise may be more significant than the ADC's quantization noise. Therefore, excessively high bit depth may not provide a substantial improvement in accuracy and can instead increase data volume and system processing complexity.

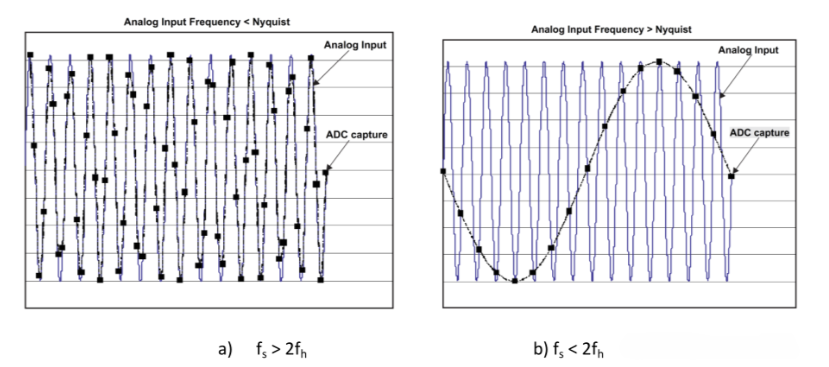

Sampling rate, expressed in Samples Per Second (SPS), defines how often the ADC samples the analog signal each second. A higher sampling rate allows the DAQ system to capture finer temporal changes in the signal, enhancing temporal resolution. According to the Nyquist Theorem, the sampling rate must be at least twice the highest frequency component present in the signal to avoid aliasing – a phenomenon where high-frequency components are misrepresented as lower frequencies. If the sampling rate falls below this requirement, signal details will be lost, leading to distorted data.

In applications such as vibration analysis, audio processing, or wireless communications, signals can change very rapidly. High sampling rates are essential to accurately capture these fast-changing characteristics. For example, in vibration monitoring, mechanical systems can vibrate at very high frequencies; low sampling rates cannot capture these high-frequency components, impairing the analysis of vibration characteristics. Similarly, in audio signal processing (e.g., recording devices or audio digitization), the sampling rate determines the level of detail captured in the sound signal. Common audio sampling rates like 44.1 kHz or 48 kHz ensure accurate reproduction of the audible frequency spectrum (roughly 20 Hz to 20 kHz). High sampling rates also allow the system to more precisely resolve the timing between two closely spaced signal events. For instance, in certain scientific experiments, signals might change within extremely short time intervals; a high sampling rate ensures these rapid changes are captured, preventing the loss of critical information.

Figure 3 Result of Insufficient Sampling Rate

However, higher sampling rates also increase data volume and processing burden. The system must balance storage space, transmission bandwidth, and processing power. For low-frequency, slowly changing signals, excessively high sampling rates offer little benefit and add unnecessary system complexity. Therefore, selecting an appropriate sampling rate during DAQ system design is crucial.

When designing a DAQ system, choosing bit depth and sampling rate requires finding a balance between precision and data volume. While high bit depth and high sampling rate enhance system performance, they also increase data storage demands. Higher ADC bit depth provides finer signal representation, ideal for precise measurements and weak signal capture. Higher sampling rates provide stronger response capabilities for fast-changing signals. Consequently, selecting the optimal parameter configuration based on the specific application is essential. This ensures measurement requirements are met without overwhelming data processing and storage capabilities, achieving the ideal measurement outcome.

Doewe Technologies is consistently committed to delivering innovative, unique, and reliable product solutions in the field of data acquisition. We deeply understand that these elements are the cornerstone for enterprises to establish themselves in the market competition. Precisely for this reason, our inspiration for innovation stems from the real application needs of our customers, not merely to showcase flashy product features. Through continuous optimization and enhancement of data acquisition solutions, Doewe Technologies empowers partners to move towards an efficient and precise future. Welcome to choose Doewe Technologies and jointly open a new chapter in data acquisition.